For the Arrow Lake Refresh cancellation, I have no basis for judging if the people they cite have a decent reputation for having inside sources (they might!) since historically I haven’t paid much attention to the rumor mill on the PC side and I almost didn’t post it because of that but since a notebookcheck picked it up I thought maybe it’s at least worth noting.

The Royal Core cancellation comes from MILD who I have heard of and see … varying opinions of but it also seems generally agreed that he may actually have sources:

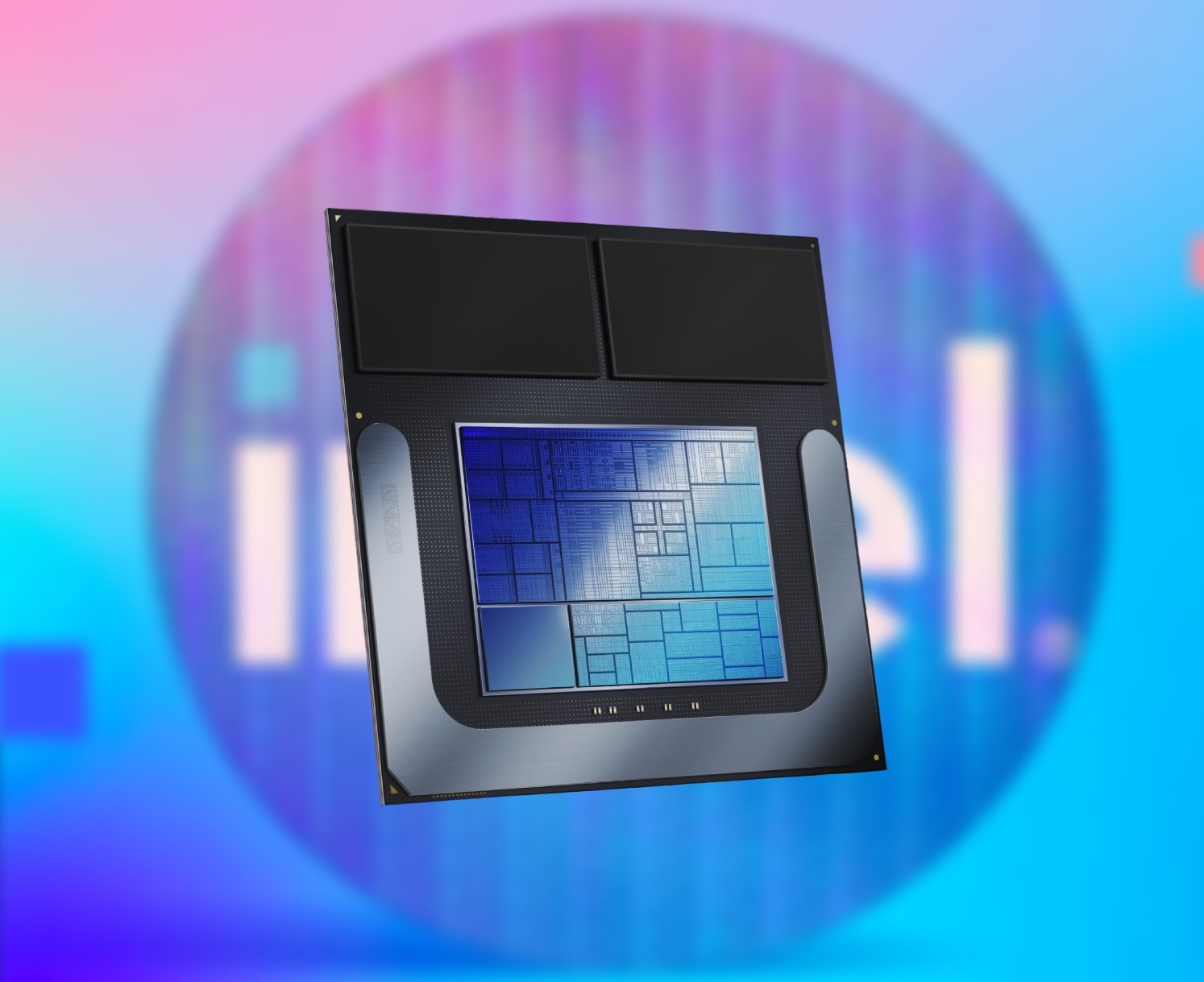

After previously leaking that Intel has canceled Beast Lake, leaker Moore's Law Is Dead has further detailed the situation around the Royal Core project. The leaker has alleged some interesting information regarding the specifications and performance of the Beast Lake and Beast Lake Next...

www.notebookcheck.net

And according to him apparently the Royal Core cancellation has to do with Gelsinger not liking the project and canning it because Intel won’t need a high performance CPU core in the future.

I have to admit the rentable unit idea as laid out here sounds kind of neat if it worked:

And according to the leak, it was working but Gelsinger killed it anyway:

Again, who knows right?

All of this from the description to the cancellation to the reason behind the cancellation could all be BS. But it’s the only piece of information we have and at least the description of rentable units sort of makes sense with what had been leaked before, maybe independently (maybe not if it’s the same source simply giving the same info to two people).