KingOfPain

Site Champ

- Joined

- Nov 10, 2021

- Posts

- 804

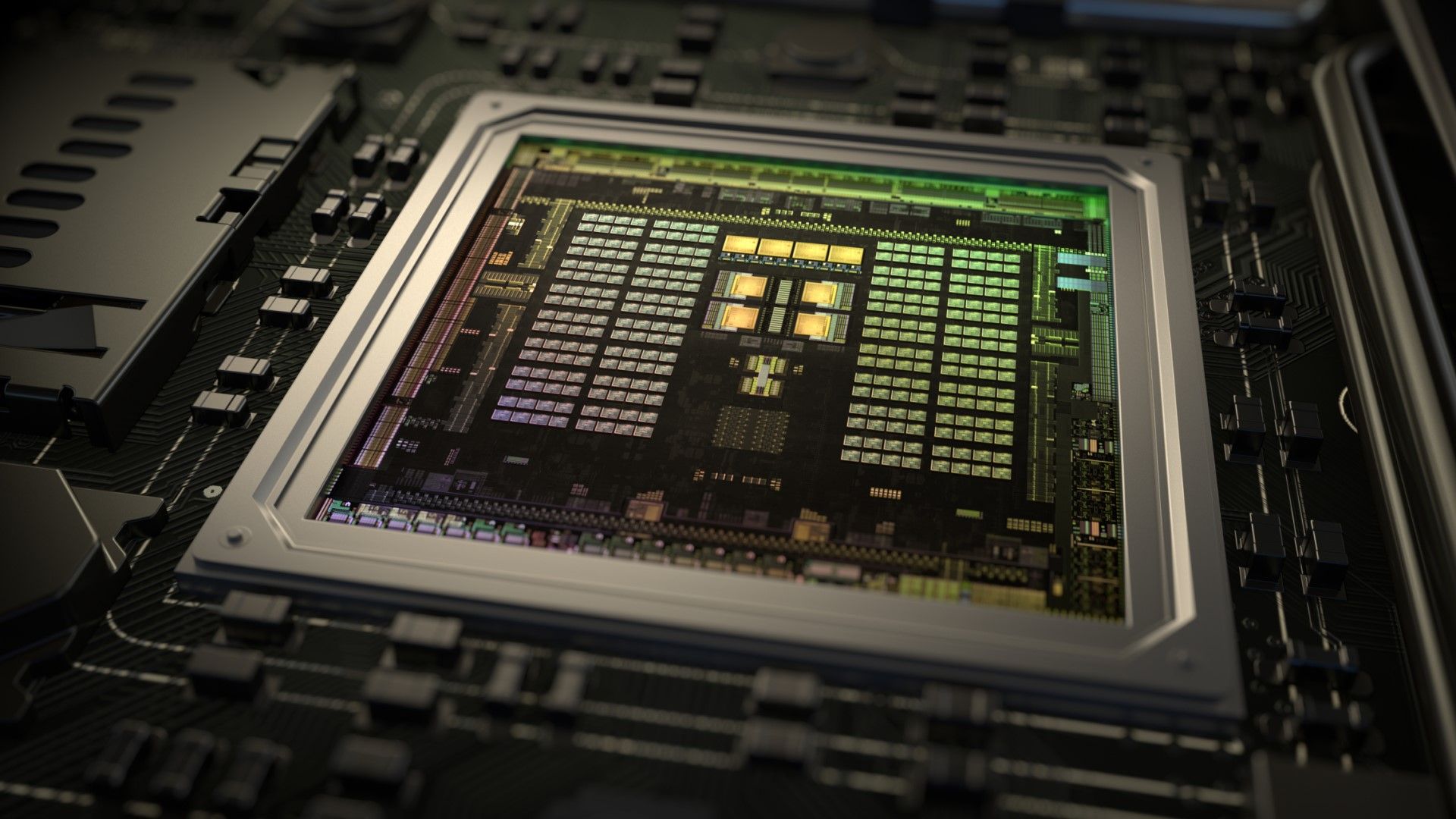

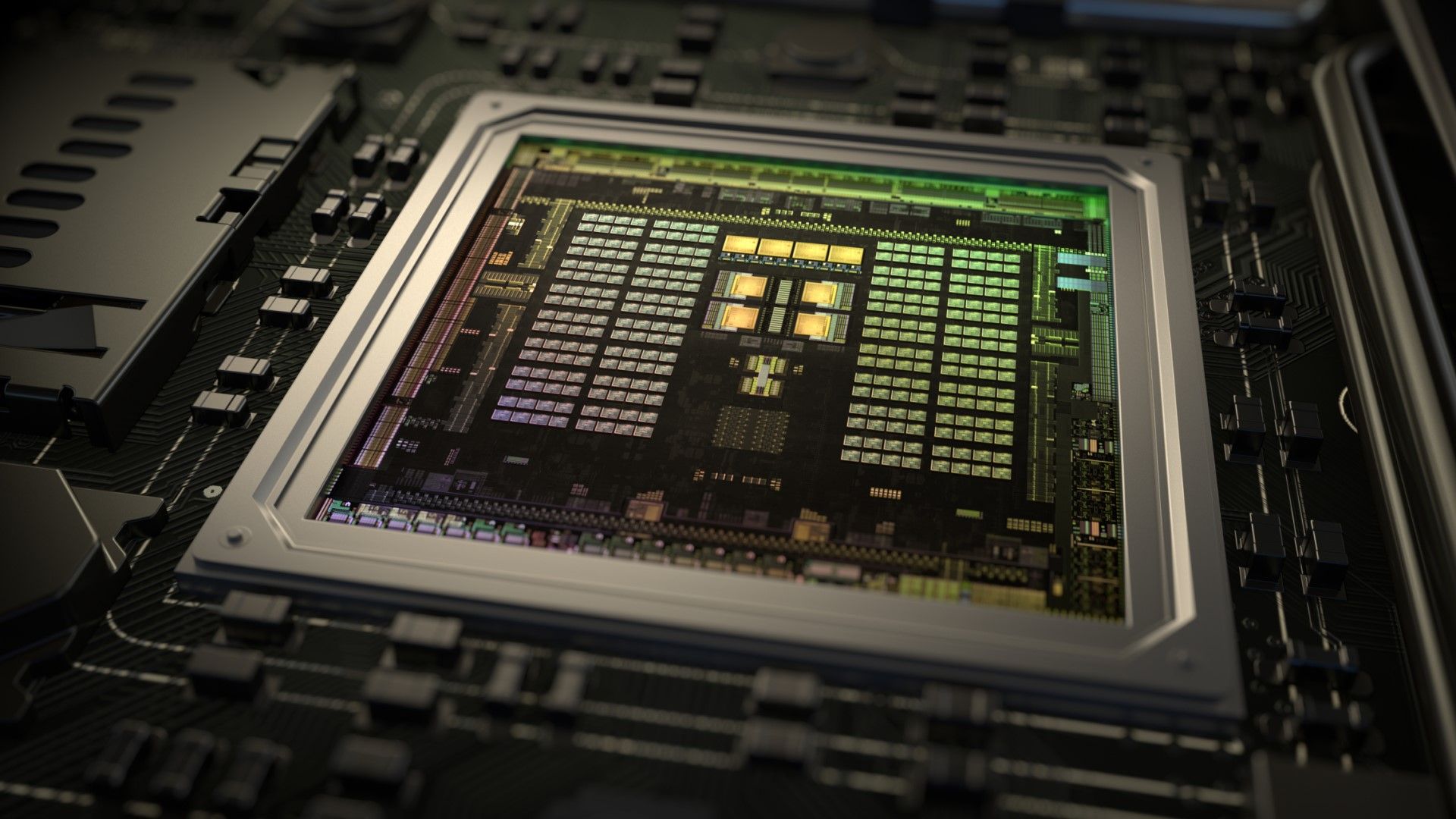

It seems with Nvidia‘s N1x there might be even more ARM-based Windows laptops on the future:

www.tomshardware.com

www.tomshardware.com

Nvidia ARM SoC for Windows machines reportedly debuting in Q4, featuring N1X, with N1 to follow in early 2026

Nvidia is gunning for the Windows PC ecosystem, competing with Intel, AMD, and Qualcomm. Will we learn more at Computex?